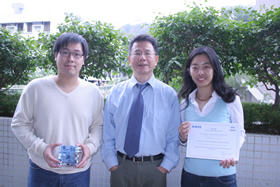

Xilinx ESL Education Board

The paper entitled “Fast Placement-Intact Logic Perturbation Targeting for FPGA Performance Improvement” was awarded a Celoxica Best Paper in the IEEE International SPL2007 conference held in Argentina on Feb. 2007. A Xilinx ESL Educational Board (a US$750 package sponsored by Celoxica Company) was awarded as a prize. Ms. Lin Zhou and Mr. Wai-Chung Tang are Ph.D. students of the Department supervised by Prof. David Wu.

Highlight of the work:

A digital circuit is basically composed of circuit elements (e.g. gates) and signal-wires interconnecting them. The circuit optimization techniques adopted by current academic and commercial Electronic Design Automation (EDA) tools are basically element-based, which were developed decades ago and unfortunately have been shown to be inaccurate for today’s deep-submicron circuits, whose signal delays are mainly (over 80%) attributed to signal wires not circuit elements. It is clearly more accurate to have a wiring-based EDA technique, rewiring, instead. Meanwhile, one unique property of an FPGA chip is that any logic perturbation inside its Look-Up-Tables (LUTs) is totally area/delay-free. This free resource can then be used to trade for LUT-external logic/wire perturbations useful for EDA improvements, an extra flexibility ignored before. Using rewiring technique for such logic perturbations, we show that significant cut-downs upon already excellent results from the state-of-the-art TVPR place-and-route can still be obtained.

This new operation can further reduce the number of LUTs by up to 33.7% (avg. 10%) without delay penalty and also reduce critical path delay by up to 31.7% (avg. 11%) without disturbing placement or sacrificing area in the final routing. For delay reduction, under proper rewiring analysis and planning, the CPU time used by rewiring can be only 5% of the total run time consumed by TVPR’s placement and routing. This idea of applying swapping between the free LUT-internal and the useful LUT-external logic perturbations is simple and proved to be powerful. The results suggest a new technique for an optimization domain unexplored for FPGA design flow.