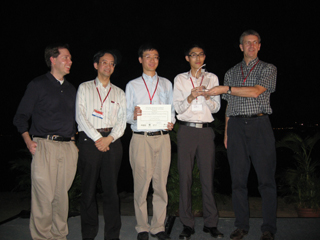

A paper by C.T. Chow, L.S.M. Tsui, P.H.W. Leong from the Department of Computer Science and Engineering, The Chinese University of Hong Kong, coauthored with W. Luk (Imperial College) and S. Wilton (University of British Columbia) was awarded the best paper award at the IEEE International Conference on Field-programmable Technology (FPT) 2005 conference in Singapore. The paper, entitled “Dynamic Voltage Scaling for Commercial FPGAs”, presents a methodology to reduce the power consumption of commercial field programmable gate array (FPGA) devices.

Paper Abstract:

A methodology for supporting dynamic voltage scaling (DVS) on commercial FPGAs is described. A logic delay measurement circuit (LDMC) is used to determine the speed of an inverter chain for various operating conditions at run time. A desired LDMC value, intended to match the critical path of the operating circuit plus a safety margin, is then chosen; a closed loop control scheme is used to maintain the desired LDMC value as chip temperature changes, by automatically adjusting the voltage applied to the FPGA. We describe experiments using this technique on various circuits at different clock frequencies and temperatures to demonstrate its utility and robustness. Power savings between 4% and 54% for the Vint supply are observed.