Project Summary

Motivation

Network-on-Chip (NoC) is generally regarded as the most promising solution for the future on-chip communication scheme in giga-scale integrated circuits (ICs). Existing verification techniques, such as simulation, formal verification, static timing analysis, and emulation cannot guarantee the correctness of the first silicon for such NoC-based systems due to its high design complexity. An effective and efficient silicon debug strategy is thus of crucial importance to its time-to-market and its success. State-of-the-art multi-core debug architectures, however, mainly target bus-based ICs, and hence are not readily applicable for NoC-based systems.

Approach

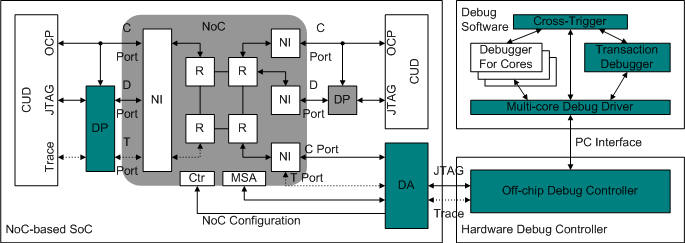

In this project, we proposed a debug platform that supports concurrent debug access to the cores under debug (CUDs) and the NoC infrastructure in a unified architecture (shown in the following figure). By introducing novel debug probes (DPs) between every CUD and its network interface (NI) and a system-level debug agent (DA) on-chip, controlled by the external debuggers running on a PC through an off-chip debug controller, the novel debug platform is supposed to provide in-depth analysis features for NoC-based systems, such as NoC transaction analysis, multi-core cross-triggering and global synchronized timestamping, with limited design-for-debug overhead in terms of device pins, silicon area and routing.

Papers and Presentations

A Multi-Core Debug Platform for NoC-Based Systems, IEEE/ACM Design, Automation, and Test in Europe (DATE), Apr. 2007.

A Debug Probe for Concurrently Debugging Multiple Embedded Cores and Inter-Core Transactions in NoC-Based Systems, IEEE/ACM Asia and South Pacific Design Automation Conference (ASP-DAC), Jan. 2008.

- Paper

- Presentation (coming soon)

In-band Cross-Trigger Event Transmission for Transaction-Based Debug, IEEE/ACM Design, Automation, and Test in Europe (DATE), March 2008.

- Paper

- Presentation (coming soon)

On Reusing Test Access Mechanisms for Debug Data Transfer in SoC Post-Silicon Validation, IEEE Asian Test Symposium (ATS), Nov. 2008.

- Paper

- Presentation (coming soon)