# MOSS: Multi-Modal Representation Learning on Sequential Circuits

Mingjun Wang<sup>1,2,3,4</sup>, Bin Sun<sup>1,3</sup>, Jianan Mu<sup>1,3</sup>, Feng Gu<sup>1,2,3,4</sup>, Boyu Han<sup>5</sup>, Tianmeng Yang<sup>6</sup>, Xinyu Zhang<sup>1,3</sup>, Silin Liu<sup>1,3</sup>, Yihan Wen<sup>7</sup>, Hui Wang<sup>4</sup>, Jun Gao<sup>4</sup>, Zhiteng Chao<sup>1,3,4</sup>, Husheng Han<sup>1,3</sup>, Zizhen Liu<sup>1,3</sup>, Shengwen Liang<sup>1,3</sup>, Jing Ye<sup>1,3,4</sup>, Bei Yu<sup>2</sup>, Xiaowei Li<sup>1,3</sup>, Huawei Li<sup>1,3</sup>

<sup>1</sup>Institute of Computing Technology, CAS <sup>2</sup>The Chinese University of Hong Kong <sup>3</sup>University of CAS <sup>4</sup>CASTEST Co., Ltd. <sup>5</sup>Stanford University <sup>6</sup>Peking University <sup>7</sup>Beijing University of Technology Corresponding authors: mujianan@ict.ac.cn, lihuawei@ict.ac.cn

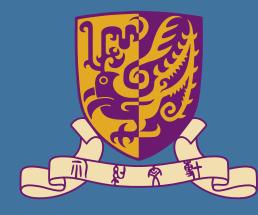

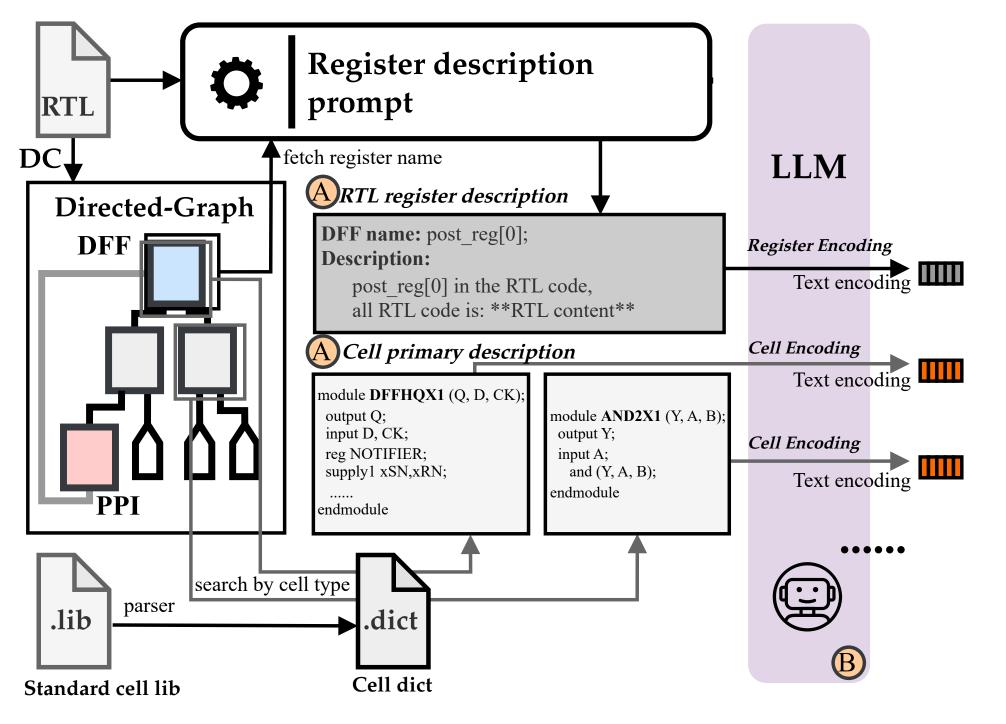

Figure 1. Overview of the MOSS framework

#### Introduction

- Deep learning has significantly advanced Electronic Design Automation (EDA), with circuit representation learning emerging as a key area

- Existing methods use either LLMs for RTL analysis or GNNs for netlist modeling

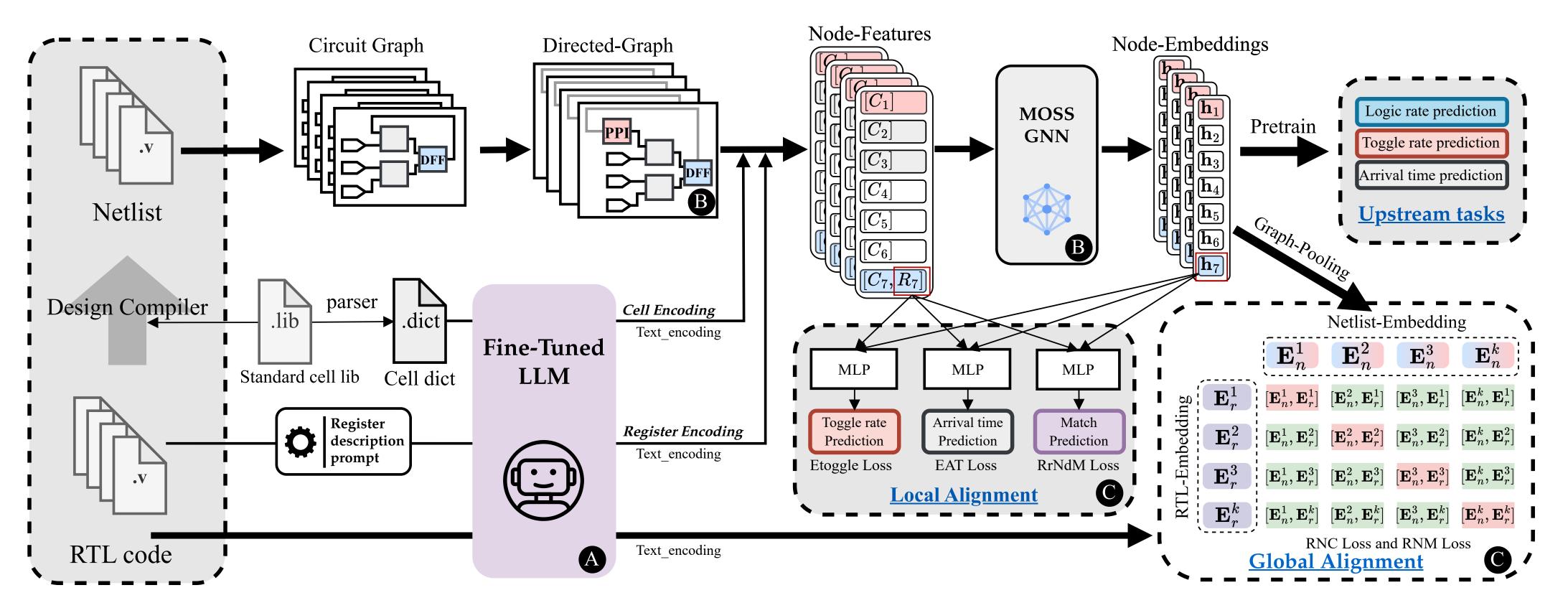

- Challenges: GNNs face difficulties with sequential circuits:

- Long-range information dependenciesInsufficient functional supervision

- Limited generalization capability

Figure 2. Challenges and motivations for sequential circuit representation learning

## Our Solution: MOSS

- Integrates GNNs with LLMs for sequential circuit modeling

- Enhances DFF node features with LLM embeddings from RTL

- Introduces adaptive aggregation and two-phase propagation

- Achieves 95.2% accuracy in arrival time prediction

## **Problem Formulation**

Sequential circuits modeled as directed graphs G = (V, E):

- V: circuit components (logic gates, DFFs)

- E: component connections

**Goal:** Learn node embeddings  $\mathbf{H} \in \mathbb{R}^{|V| \times d}$  that encode both structural and temporal features:

$$\mathbf{H} = f(G, \mathbf{X}, \mathbf{T}) = f(V, E, \mathbf{X}, \mathbf{T}) \tag{}$$

where  ${\bf X}$  represents structural features and  ${\bf T}$  represents temporal features.

## Key Tasks:

- Toggle rate/Power prediction

- Arrival time prediction

- Functional equivalence checking

# **MOSS Framework Overview**

## **Key Components:**

- 1. **LLM-Enhanced Node Features:** Fine-tuned LLM generates contextual embeddings for DFF nodes

- 2. **Graph Construction:** Netlist represented as directed graph with adaptive aggregators

- 3. Local & Global Alignment: Multi-task learning with specialized loss functions

#### **Technical Innovations**

#### 1. LLM Fine-Tuning and Feature Enhancement

- Fine-tuned Yi-Coder-9B-Chat on 31,701 RTL descriptions

- Extract contextual embeddings for registers and logic cells

- Mean pooling to aggregate token embeddings

Figure 3. LLM feature extraction process

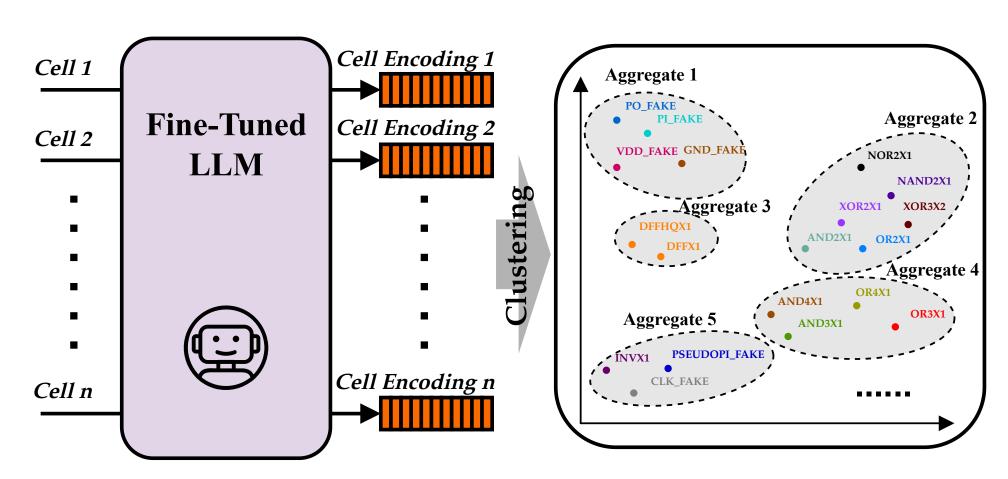

## 2. Adaptive Aggregator Design

- DBSCAN clustering based on LLM embeddings

- Different attention-based aggregators for each cell category

- Automatically adapts to various cell types

Figure 4. Adaptive aggregator with clustering

## 3. Two-Phase Propagation Mechanism

- Phase 1: Forward propagation from Pls to DFFs

- Phase 2: Turnaround propagation for feedback loops

- Asynchronous updates to model signal propagation

## **Experimental Results**

**Dataset:** 31,701 RTL designs synthesized with Synopsys DC Circuit sizes: 100 to 5,000 cells

Table 1. Performance comparison on various metrics (%)

|   | Circuit      | DeepSeq2 |      |      | MOSS w/o FAA |      |      | MOSS w/o AA |      |      | MOSS w/o A |      |      | MOSS |      |      |

|---|--------------|----------|------|------|--------------|------|------|-------------|------|------|------------|------|------|------|------|------|

|   |              | ATP      | TRP  | PP   | ATP          | TRP  | PP   | ATP         | TRP  | PP   | ATP        | TRP  | PP   | ATP  | TRP  | PP   |

|   | max_selector | 81.4     | 78.7 | 94.6 | 47.0         | 75.8 | 88.6 | 82.3        | 85.2 | 94.5 | 95.4       | 89.4 | 99.9 | 95.6 | 90.5 | 99.9 |

|   | pipeline_reg | 77.6     | 83.6 | 91.4 | 52.2         | 63.6 | 63.4 | 80.5        | 88.3 | 90.2 | 94.2       | 92.1 | 94.1 | 94.5 | 92.4 | 94.6 |

| ľ | mult_16x32   | 57.6     | 66.6 | 80.1 | 19.3         | 40.1 | 54.1 | 75.2        | 72.3 | 85.4 | 93.9       | 84.8 | 91.5 | 94.3 | 87.9 | 93.  |

|   | Average      | 79.1     | 76.4 | 88.4 | 45.6         | 57.1 | 75.1 | 80.3        | 81.0 | 90.7 | 94.9       | 87.0 | 95.1 | 95.2 | 87.5 | 96.3 |

#### Key Findings:

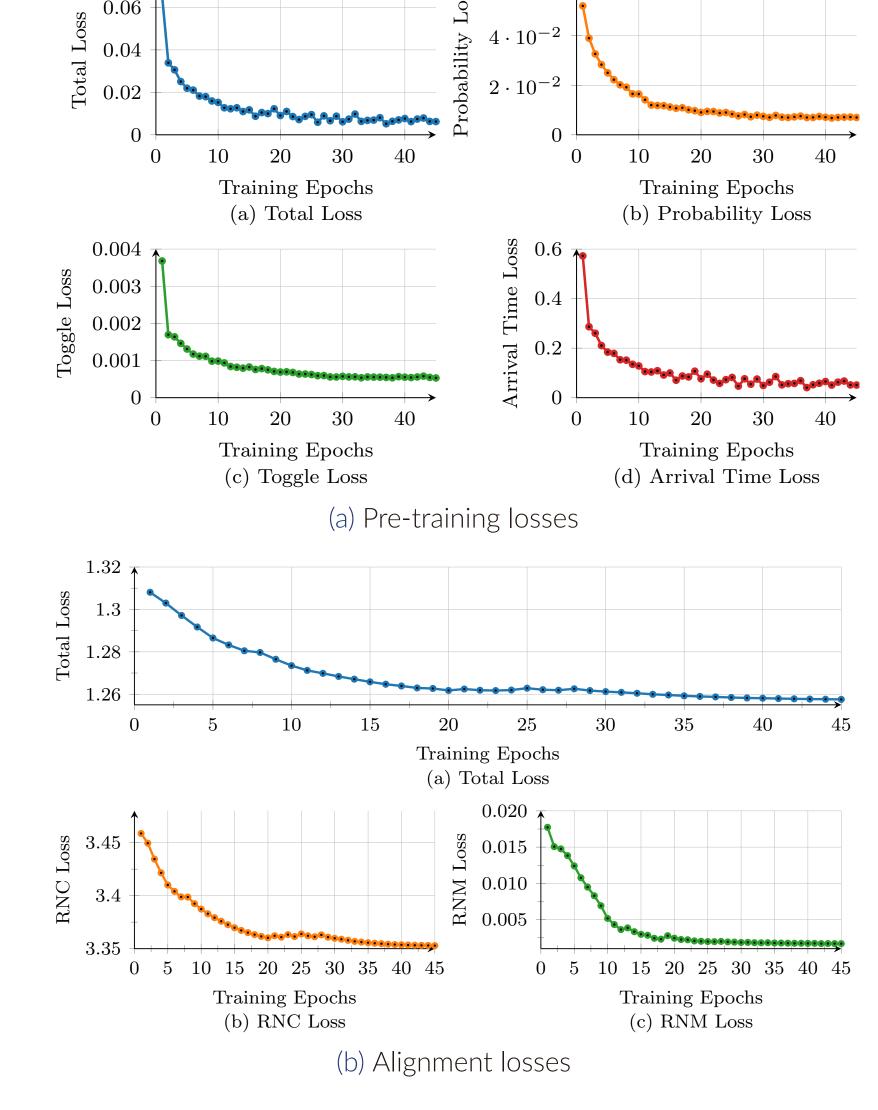

- MOSS achieves 95.2% accuracy in arrival time prediction and leads with 96.3% accuracy for power prediction.

- Significant improvement on larger circuits (e.g., mult\_16x32: 94.3% vs 57.6%)

- Superior performance in functional equivalence checking (93.7% average)

Figure 5. Training loss curves showing effective convergence

## Ablation Study Results:

- LLM features crucial: MOSS w/o FAA drops to 45.6% ATP

- Alignment important for FEP: 93.7%  $\rightarrow$  26.6% without alignment

- Adaptive aggregator improves all metrics

## Conclusion

- First multimodal framework combining GNNs and LLMs for sequential circuits

- Novel techniques: LLM-enhanced DFF features, adaptive aggregation, two-phase propagation

- Superior performance: Experimental results show that MOSS significantly boosts accuracy for tasks like toggle rate and arrival time prediction—95.2% arrival time prediction accuracy

- Addresses key challenges: Long-range dependencies and functional supervision

- Future impact: Opens new directions for AI-driven EDA research and multimodal EDA prediction

## Acknowledgements

This work is supported by the Chinese Academy of Sciences (XDB0660102) and NSFC (62090024).