## CENG4480 Homework 3

Due: Dec. 09, 2018

## **Solutions**

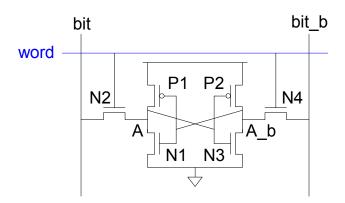

**Q1** Given the 6T-SRAM cell as in Figure 1, discuss the reading behavior (i.e., reading steps) if originally A = 1, A\_b = 0.

Figure 1: 6T-SRAM cell structure.

- A1 (Please follow the the notes in slides)

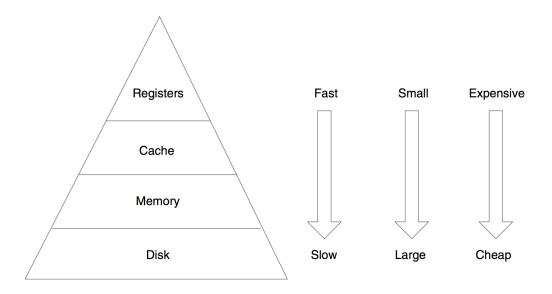

- Q2 What is the modern memory hierarchy? Analysis the properties of each hierarchy level.

- A2 (Analyze based on the following figure:)

1. On-Chip Register; L1, L2 Cache; Main Memory; Secondary Storage (Disk).

## 2. Working speed decrease and storage size increase along above hierarchy level.

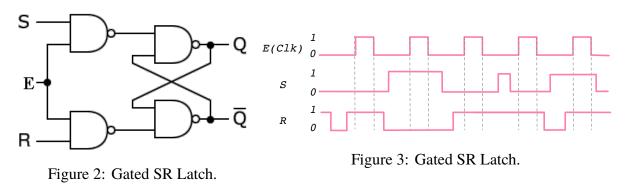

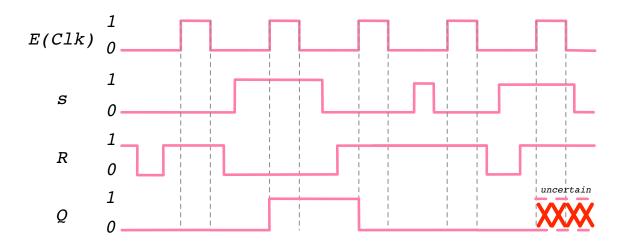

Q3 For the given SR Latch in Figure 2. Assume the initial state of  $\bar{Q}$  is 1. Try to draw the waveform of Q if S, R, and E(Clk) have shown in Figure 3.

A3 The waveform is shown as in the following figure:

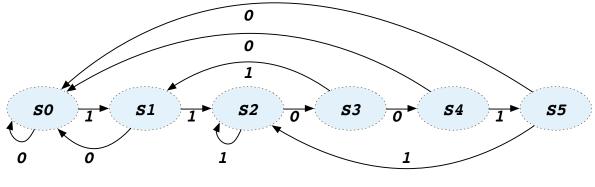

- Q4 Design a finite state machine to detect the pattern of "11001" in the bit stream. How many states are required? Draw the state transition graph.

- A4 The state transition graph is shown in the following figure:

You can also draw the **state transition table** as follows<sup>1</sup>:

| State      | Coding  | Current State | Input | Next State |

|------------|---------|---------------|-------|------------|

| <b>S</b> 0 | Initial | SO            | 0/1   | S0/S1      |

| <b>S</b> 1 | 1       | <b>S</b> 1    | 0/1   | S0/S2      |

| S2         | 11      | <b>S</b> 2    | 0/1   | S3/S2      |

| <b>S</b> 3 | 110     | <b>S</b> 3    | 0/1   | S4/S1      |

| S4         | 1100    | <b>S</b> 4    | 0/1   | S0/S5      |

| S5         | 11001   | S5            | 0/1   | S0/S2      |

<sup>&</sup>lt;sup>1</sup>Note: state transition graph and state transition table are equivalent, thus you only need to provide one.

Figure 4: A4

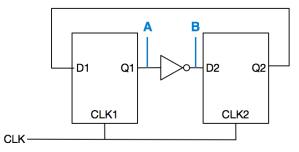

Q5 A digital clock is important in circuit design. Please answer the following **three** questions. (a) Given the following circuit  $CLK_1 = CLK_2 = 25MH_2$ : Tff = 5nc; Testup = 5nc. The

(a) Given the following circuit, CLK1 = CLK2 = 25MHz; Tff = 5ns; Tsetup = 5ns. The gate delay TG = 10ns. Please calculate the time margin. Note: Tff= delay of a flip flop, Tsetup=setup time of a flip flop, and TG is delay of a gate.

(b) In the above circuit, currently there is already one delay gate with delay TG. How many more similar delay gates can you insert between A and B without creating error?

(c) Sometimes we can take advantage of clock skew. For the above circuit, if the delay from CLK to CLK2 is 4ns, calculate the minimal clock period of the clock CLK.

A5 1. Period =

$$\frac{1}{25M}$$

= 40ns. Margin = 40 - 5 - 5 - 10 = 20ns

20

2. Max #gate =  $\frac{20}{10}$  = 2. So 2 more gates can be inserted.

3. Since we are searching for minimal period, no slack is desired.

$$Tc1 + Tff + TG + Tsetup = TCLK + Tc2$$

(1)

From Equation (1) we have TCLK = 20 + Tc1 - Tc2. We set Tc1 = 0, then we can obtain TCLK = 16ns