# HW1 Review

LIU Hongduo CSE Department, CUHK hdliu21@cse.cuhk.edu.hk

Spring 2022

Assume a 20 cm diameter wafer has a cost of 15, contains 100 dies, and has 0.030 defects/cm<sup>2</sup>.

- **1** Find the yield of this wafer.

- 2 Find the cost per die for this wafer.

## **Related Course Contents**

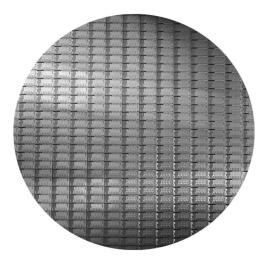

A 12-inch (300 mm) wafer of Intel Core i7 (Courtesy Intel).

#### wafer

A slice composed of silicon, used to create chips.

#### die

The individual rectangular sections that are cut from a wafer, more informally known as chips.

#### defect

A microscopic flaw in a wafer that can result in the failure of the die containing that defect.

#### yield

The percentage of good dies from the total number of dies on the wafer.

Die area

$$\approx \frac{\text{Wafer area}}{\text{Dies per wafer}}$$

(1)

This equation is an approximation, since the area near the border of the wafer **cannot** accommodate the rectangular dies. According to equation Equation (1), Die area  $\approx \frac{\pi \times (\frac{20}{2})^2}{100} \approx 3.14$ cm<sup>2</sup>

$$Yield = \frac{1}{(1 + \frac{\text{Defects per area \times Die area}}{2})^2}$$

(2)

This equation is based on empirical observations of yields at the integrated circuit factories. According to equation Equation (2), Yield  $= \frac{1}{(1+\frac{0.030\times3.14}{2})^2} = 0.9121.$

(3)

Cost per die =

$$\frac{\text{Cost per wafer}}{\text{Dies per wafer } \times \text{ yield}}$$

According to Equation (3), Cost per die =  $\frac{15}{100 \times 0.9121} = 0.1645$ .

Suppose we developed a new processor that has 75% of the capacitive load of the older processor. Also it can reduce voltage 20% compared to previous generation. What is the impact on dynamic power if the frequency keeps unchanged? Give the ratio of  $\frac{Power_{new process}}{Power_{old processor}}$ .

$$Power = \frac{1}{2} \times \alpha \times Capacitive \ load \times Voltage^2 \times Frequency \ switched \qquad (4)$$

According to Equation (4),  $\frac{Power_{new}}{Power_{old}} = 0.48$ .

For the following C statement, write the corresponding RISC-V assembly code. Assume that the C variables f, g, and h, have already been placed in registers  $\times 5$ ,  $\times 6$ , and  $\times 7$  respectively. Use a minimal number of RISC-V assembly instructions.

$$f = g + (h-8)$$

#### As shown below,

- 1 addi x5, x7, -8

- 2 add x5, x5, x6

#### Assume the following register contents:

x5 = 0xAAAAAAA, x6 = 0x12345678

1. For the register values shown above, what is the value of x7 for the following sequence of instructions?

slli x7, x5, 4 or x7, x7, x6

2. For the register values shown above, what is the value of  $\times 7$  for the following sequence of instructions?

srli x7, x5, 3

andi x7, x7, 0xFEF

#### 1. 0xbabefef8

2. When we treat OxFEF as 0x00000FEF, the answer is 0x545. When we treat OxFEF as 0xFFFFFFEF, the answer is 0x15555545. In general, the immediate of andi instruction will be signed-extended to 12 bits. Since here is an ambiguity, we accept both solutions when grading. Please note that when we actually run the code in RARS simulator, the RARS simulator treats the immediate 0xFEF as an unsigned value 4079 and sign-extents it to a 12-bit value will cause an error.

| 1  | .globl _start      |

|----|--------------------|

|    | .data              |

|    | .text              |

|    | _start:            |

| 5  | Li að, ÖXAAAAAAA   |

| 6  | srli a0, a0, 3     |

| 7  | andi a0, a0, 0xFEF |

| é  |                    |

|    |                    |

| 10 |                    |

| 11 |                    |

|    |                    |

| 12 |                    |

| 13 |                    |

Clear

Run the code directly in RARS simulator

| -      |            |            |                |            |            |             | Taut       | Seament           |           |                    |           |              |           |             |           |            |      | Name | Num Value      |

|--------|------------|------------|----------------|------------|------------|-------------|------------|-------------------|-----------|--------------------|-----------|--------------|-----------|-------------|-----------|------------|------|------|----------------|

| 00     | •          |            |                |            |            |             | Text       | segment           |           |                    |           |              |           |             |           |            | _    | zero | 9 9×999999999  |

| Bkpt   |            | Code       | Basic          |            | Source     |             |            |                   |           |                    |           |              |           |             |           |            |      | ra   | 1 0×00000000   |

|        |            |            | lui x10,0xfff; |            | 5:         | li a0       | 0xAAAAA    | AAAA              |           |                    |           |              |           |             |           |            |      | SD   | 2 0x7fffeffc   |

|        |            |            | addi x10,x10,  |            |            |             |            |                   |           |                    |           |              |           |             |           |            |      | gp   | 3 0×10008000   |

|        | 0x00400008 | 0x00355513 | srli x10,x10,  | 3          | 6:         | srli a      | a0, a0, 1  | 3                 |           |                    |           |              |           |             |           |            |      | tp   | 4 0×00000000   |

|        | 0x0040000c | Øxfef57513 | andi x10,x10,  | Øxffffffef | 7:         | andi a      | a0, a0, I  | <b>3xFFFFFFFF</b> |           |                    |           |              |           |             |           |            |      | tø   | 5 0x00000000   |

|        |            |            |                |            |            |             |            |                   |           |                    |           |              |           |             |           |            |      | t1   | 6 0x00000000   |

|        |            |            |                |            |            |             |            |                   |           |                    |           |              |           |             |           |            |      | t2   | 7 8x888888888  |

|        |            |            |                |            |            |             |            |                   |           |                    |           |              |           |             |           |            |      | 50   | 8 0x00000000   |

|        |            |            |                |            |            |             |            |                   |           |                    |           |              |           |             |           |            |      | s1   | 9 8×88888888   |

|        |            |            |                |            |            |             |            |                   |           |                    |           |              |           |             |           |            |      | aØ   | 10 0x15555545  |

|        |            |            |                |            |            |             |            |                   |           |                    |           |              |           |             |           |            |      | a1   | 11 0×00000000  |

|        |            |            |                |            |            |             |            |                   |           |                    |           |              |           |             |           |            |      | a2   | 12 0×00000000  |

| _      |            |            |                |            |            |             |            |                   |           |                    |           |              |           |             |           |            | _    | a3   | 13 0×00000000  |

| 00     |            |            |                |            |            |             | Data       | Seament           |           |                    |           |              |           |             |           |            |      | a4   | 14 0x00000000  |

| Addres |            | Value (+0) | Value (        | 1.45       | Value (+8) |             | Value (+c) |                   | Value (+1 | 20                 | Value (+1 | 4)           | Value (+1 | 193         | Value (+1 | 43         | - 11 | a5   | 15 0×00000000  |

| Auures | 0×1001000  |            | 00000000       | 0×00000000 |            | 3×886688866 |            | x008666886        |           | 9,<br>9×8999988999 |           | 9x080000800  |           | 0x00000000  |           | 0×80008800 |      | a6   | 16 0x00000000  |

|        | 0.1001000  |            | 00000000       | 0000000000 |            | 3           |            |                   |           | 00000000000        |           | 0.0000000000 |           | 0.000000000 |           | 0000000000 |      | 97   | 17 8x886688866 |

#### Treat OxFEF as OxFFFFFFFF

# Q5 Description

#### Consider the following RISC-V loop:

```

LOOP: beq x6, x0, DONE

addi x6, x6, -1

addi x5, x5, 2

jal x0, LOOP

DONE:

```

- Assume that the register x6 is initialized to the value 10. What is the final value in register x5 assuming the x5 is initially zero?

- 2 For the loop above, write the equivalent C code. Assume that the registers x5 and x6 are integers acc and i, respectively.

- For the loop written in RISC-V assembly above, assume that the register x6 is initialized to the value *N*. How many RISC-V instructions are executed?

- G For the loop written in RISC-V assembly above, replace the instruction "beq x6, x0, DONE" with the instruction "blt x6, x0, DONE" and write the equivalent C code.

### 1 20

while (i != 0) {

acc += 2;

i = i-1; }

#### **3** 4N+1

```

4 while (i >= 0) {

acc += 2;

i = i-1; }

```

Some RISC-V assembly instructions are shown below. Assume that the variables f, g are assigned to registers  $\times 5$ ,  $\times 6$ , respectively. Assume that the base address of the arrays A and B are in registers  $\times 10$  and  $\times 11$ , respectively.

slli x30, x5, 2 // x30 = f\*4

add x30, x10, x30 // x30 = &A[f]

slli x31, x6, 2 // x31 = g\*4

add x31, x11, x31 // x31 = &B[g]

lw x5, 0(x30) // x5 = A[f]

addi x12, x30, 4

lw x30, 0(x12)

add x30, x30, x5

sw x30, 0(x31)

- **1** What's the meaning of the last four instructions.

- 2 What is corresponding C statement?

- 1 addi x12, x30, 4 // x12 = &A[f]+4 (i.e. &A[f+1]) lw x30, 0(x12) // x30 = A[f+1] add x30, x30, x5 // x30 = A[f+1] + A[f] sw x30, 0(x31) // B[g] = x30 (i.e. A[f+1] + A[f])

- 2 The corresponding C code is: B[g] = A[f] + A[f+1]