## CENG 3420 Midterm (2018 Spring)

| Name: |  |

|-------|--|

| ID:   |  |

## Q1 (20%) Check or fill the correct answer:

- 1. Temporal / Spatial locality keeps recently accessed data items closer to the processor.

- 2. Drive strength of a gate can be increased by reducing resistance / capacitance.

- 3. Name 3 instructions that can do branch \_\_\_\_\_, \_\_\_ and \_\_\_\_

- 4. MIPS stack address grows from low / high to low / high.

- 5. As one of the evaluation metrics of computer, throughput / CPI is defined by the total amount of work done in a given time.

- 6. A flip-flop is level-sensitive / edge-triggered.

- 7. There are 3 mapping strategies in cache design, <u>direct / fully-associative / set-associative</u> mapping is widely used in current CPU design.

**Q2** (15%) Following problems assume that logic blocks needed to implement a processor's datapath has the following latencies:

| Item         | I-Mem | Add | Mux | ALU | Regs | D-Mem | Sign-Extend | Shift-Left-2 |

|--------------|-------|-----|-----|-----|------|-------|-------------|--------------|

| Latency (ps) | 200   | 70  | 20  | 90  | 90   | 250   | 15          | 10           |

- 1. If the only thing we need to do in a processor is fetch consecutive instructions (Figure 1), what would the cycle time be?

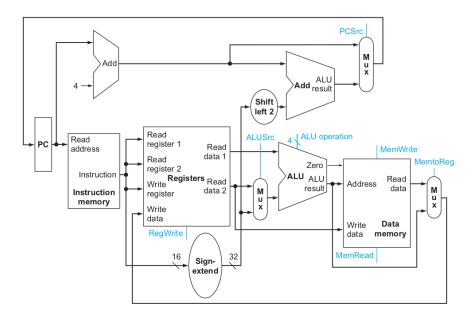

- 2. Consider a datapath similar to the one in Figure 2, but for a processor that only has one type of instruction: unconditional PC-relative branch. What would the cycle time be for this datapath?

- 3. Repeat 2, but this time we need to support only conditional PC-relative branches.

Figure 1: A portion of the datapath used for fetching instructions and incrementing the program counter.

Figure 2: The simple datapath for the core MIPS architecture combines the elements required by different instruction classes.

Table 1: Question 3

| Stages         | IF  | ID  | EX  | MEM | WB  |

|----------------|-----|-----|-----|-----|-----|

| Latencies (ps) | 200 | 170 | 220 | 210 | 150 |

- **Q3** (15%) Given the following specs of the datapath latencies:

- 1. What is the clock cycle time in a pipelined and non-pipelined processor?

- 2. What is the total latency of an LW instruction in a pipelined and non-pipelined processor?

- 3. If we can split one stage of the pipelined datapath into two new stages, each with half the latency of the original stage, which stage would you split and what is the new clock cycle time of the processor?

- **Q4** (10%) Consider a 4-block empty Cache, and all blocks initially marked as not valid, Given the main memory word addresses "4 1 2 0 4 3 7 2", calculate Cache hit rate.

- **Q5** (10%) A program runs in 10 s on computer A with 2 GHz clock. If we want to design a computer B such that the same program can be finished in 10 s, determine the clock frequency of computer B. Assume it requires 1.5× clock cycles to execute the program on computer B due to different CPU design.

- **Q6** (20%) Consider a single-level cache with an access time of 2.5 ns, a line size of 64 bytes, and a hit ratio of H = 0.95. Main memory uses a block transfer capability that has a firstword (4 bytes) access time of 50 ns and an access time of 5 ns for each word thereafter.

- 1. What is the access time when there is a cache miss?

- 2. Suppose that increasing the line size to 128 bytes increases the *H* to 0.97. Does this reduce the average memory access time?

- $\mathbf{Q7}$  (10%) You are required to develop some simple measures of pipeline performance and relative speedup.

- 1. Let  $T_{k,n}$  be the total time required for a pipeline with k stages to execute n instructions. Speedup of k stage pipeline is given by,

$$S_k = \frac{T_{1,n}}{T_{k,n}}. (1)$$

Determine  $S_k$  in terms of k and n.

2. Consider an instruction sequence of length n that is streaming through the instruction pipeline. Let p be the probability of encountering a conditional or unconditional branch instruction, and let q be the probability that execution of a branch instruction I causes a jump to a nonconsecutive address. Assume that each such jump requires the pipeline to be cleared, destroying all ongoing instruction processing, when I emerges from the last stage. Determine  $S_k$  in terms of k, n, p and q.